With UVM http://www.uvmworld.org/ adding a good framework around SystemVerilog, several ASIC design teams have taken the first step in adopting it in full form. Many are migrating from either OVM or VMM and many others are plain SystemVerilog and/or Verilog users.

One of the significant changes in latest UVM (1.1 onwards) is the so called “phasing” – it is a feature motivated from VMM users and more HW related requirement overlaid on top of more SW centric OVM-like phasing. Refer to a detailed paper on this topic from Intel + CVC @ SNUG India 2011 via: http://bit.ly/JL9x30

A direct impact of this new phasing in UVM 1.1 is that a smooth running test in OVM/plain SystemVerilog is likely terminate “prematurely” in UVM. This is typical when a first time user adds a UVM test as below:

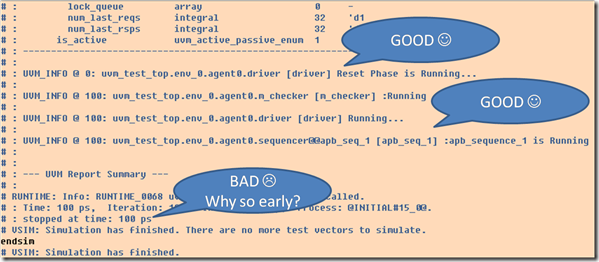

While everything seems normal as in OVM, here is a sample run.log from this test:

The new phasing seems to be in effect :

- – the reset_phase is kicking and takes its sweet 100 ns of simulation time.

- Sequence starts off

- But hold on.. why on earth is it exiting? Aren’t you supposed to run/execute that sequence for me?

The crux of this has to with the so called run time semantics of “task based phases” in UVM base class library. For those interested, here is a snippet of that documentation:

// Task: main_phase

//

// The <main_phase> phase implementation method.

//

// This task returning or not does not indicate the end

// or persistence of this phase.

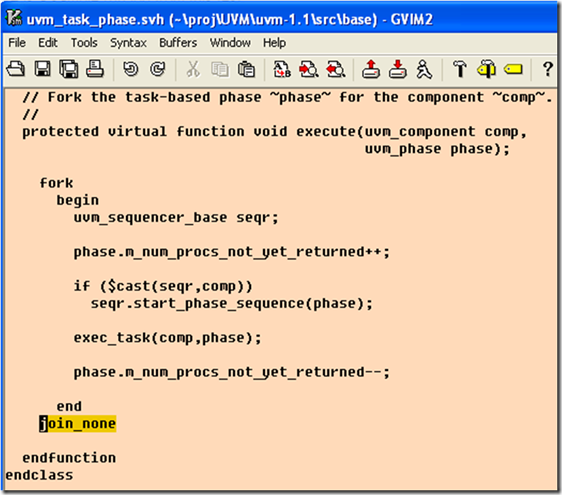

And at implementation level, here is what a relevant piece of UVM base class code that does it for you:

Now you say Aha! That explains why my test::main_phase didn’t wait for “seq.start” to finish.

Now you may ask why and more interestingly is it a BUG in UVM? Not really, this is intended, read more of UVM code/doc:

//

// Task: main_phase

//

// The <main_phase> phase implementation method.

//

// This task returning or not does not indicate the end

// or persistence of this phase.

It is necessary to raise an objection

// using ~phase.raise_objection()~ to cause the phase to persist.

// Once all components have dropped their respective objection

// using ~phase.drop_objection()~, or if no components raises an

// objection, the phase is ended.

//

Now that you understand why it happens, here is the fix for it:

Happy UVM-ing. Do call us for quick ramp-up of yourself/your team, we have some great training sessions on the same at: http://www.cvcblr.com/trainings

No comments:

Post a Comment