With DAC around the corner, it is time to update our readers on what’s new in Verification in 2012 from EDA perspective. Here is what our TeamCVC have found so far as interesting, will be glad to add more if you drop us a note via info@cvcblr.com or as comments here in this blog itself!

Here is an alphabetical order of various vendors & their solutions.

AgniSys – your neighborhood automation solution for registers & more

If your design is all about IPs and sub-systems with say,more than 50 registers – you would be using one of the several formats (standard/proprietary) to define, maintain and manage the ever changing fields/blocks etc. If you have to manually code these registers in SystemVerilog/VMM/OVM/UVM/eRM – you know how hard it is, how laborious it is and how many hours it consumes to keep them upto-date. This is precisely where AgniSys fits into your flow. Basically their IDesignSpec is a plug-in to Word/XL/FrameMaker etc. to create register specification in various formats of your choice. Here is what it can do (picture below):

If you thought it can only be for Verification team, be ready for more: it generates:

- RTL code (for Reg RD/WR)

- C-headers for SW team

- UVM/VMM/OVM code for Verif teams

- Assertions

- Functional coverage etc.

All this and more for almost free – Yes indeed! They now offer a free version of their popular IDS for even “commercial use” – see: http://www.agnisys.com/products/66-idsfree

Aldec’s Riviera-Pro brings UVM, OVM & VMM to desktop & on Cloud!

If you thought all the buzz around SystemVerilog, VMM/OVM/UVM is all for ASIC folks on Linux alone, be ready for some pleasant surprise! Aldec with its much praised easy-to-use tools like Active-HDL, ALINT etc. has built Riviera-Pro to bring these technologies to your laptops/desktops under Windows (and Linux of-course). Their intuitive debug and code-entry features are now available for SystemVerilog/UVM too. Do visit them at their booth or register via:http://www.aldec.com/en/events/sessions/38 to learn more about their debug features such as Transaction Recording, message displays etc.

Also they recently introduced Aldec Cloud – perhaps a bold step towards UVM on cloud!

Checkout their free trial @ http://www.aldec.com/en/solutions/functional_verification/aldec_cloud

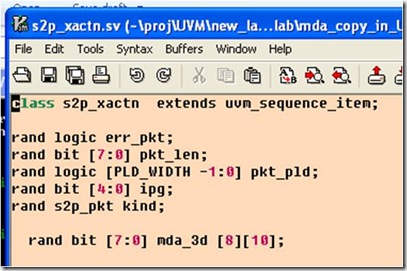

Axiom’s MPSim & DesignerUVM – the latest in UVM tools!

If you were following the availability of multi-threaded simulators in the market, it is quite possible that you had noticed the front runner in this space – the MPSim from Axiom. MPSim was the very first one to address the multi-core simulations in EDA domain and since then have grown leaps and bounds to become a strong SystemVerilog simulator with all methodologies such as VMM/OVM and UVM. It also has low power features like UPF that makes it a very compelling product for ASIC houses with large simulation requirements. Axiom is known for performance, but not just that!. It is infact their added debug capability that makes them even more compelling alternative to other vendors. In this Video interview, Tarak from Axiom explains their new debug feature DesignerUVM.

Quoting Tarak: “You can do lot of simulations, but ultimately the engineering productivity comes from the ability to debug designs”:

We couldn’t agree more! It is Debug that takes whole lot of time and it is quite unfortunate major EDA vendors have not focused their R&D energy on this as much as they perhaps should. Consider the following scenarios in UVM environments:

- A factory override didn’t occur/work as you expected it to

- get_config_string failed to fecth correct value

- In an array of virtual interfaces being hooked up to physical interfaces, something went wrong and you observe incorrect drives/samples

- Port-to-export connections seem wrong

Does your existing Debugger(s) assist you in finding this? (besides gvim/Emacs, find, grep etc.)? If not – it is time to wake up and yell for more from your vendor. Now they have a reason to listen to you – as otherwise YOU as a customer have an alternate – the Axiom DesignerUVM will do these for you!

Breker Systems – SoC level verification

Breker with its new TrekSoC is one of the hottest EDA solutions to watch for – given the huge increase in number of System-On-Chips (SoC) being designed/integrated. Ask yourself:

- How long can you continue with manually written C-tests?

- How long can you maintain 2 (or more) test-env

- One for Transaction/UVM based and

- Another for the actual processor RTL based, that require C-tests?

- What about multi-threaded tests? Can we even write them by hand and synchronize?

- Won’t it be nice to have a “single source” for both TXN tests & C-tests?

- Can we truly “reuse” knowledge from IP DITL (Day In The Life) to SoC?

- Can we quickly reproduce SoC level issues at IP level with know extra effort?

These are just some of the “tip-of-the-iceberg” problems of SoC level verification that Breker is attempting to solve for you! For sure you don’t want to miss this – if you are in SoC world (who isn’t BTW?)

Cadence’s AVIP – Accelerated VIP, next form of “Synthesizable VIP”?

For quite a while the industry has been talking about “Synthesizable VIPs” for the want of putting them into FPGAs/Emulators and get more cycles out of DV tasks. VMM started it with VMM-HAL, then came the flurry of Virtual prototypes/platforms that promise to allow smooth integration of various abstraction models in a simulation/emulation env. Cadence’s recent announcement on AVIP is worth noting in this space, see them at DAC for more.

Mentor’s UVM Express, UVMConnect & more..

Mentor recently announced their extended UVM initiatives via UVM Express & UVM Connect:

Their Verification Academy initiative continues to be very popular among users, even non-Mentor customers. Hats off to Dave Rich for keeping the quality of discussions/responses very neutral and technical!

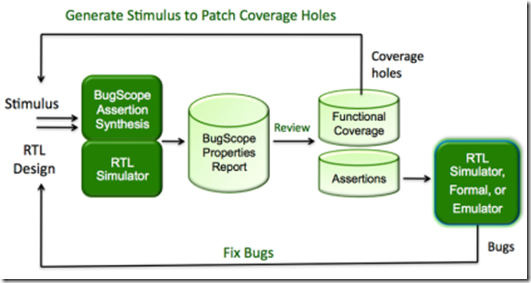

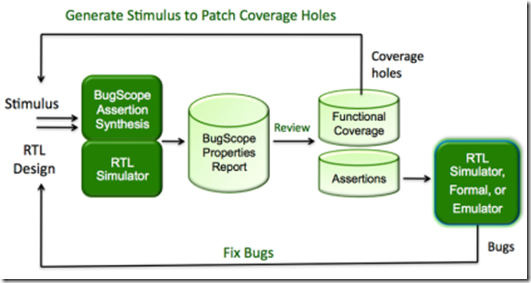

NextOp – Assertion Synthesis/Mesh generation

Whether you are doing IP level verification, sub-system or SoC – assertions are your friends – to detect bugs close to the source, apply formal search, indicate coverage holes etc. One of the biggest challenges in adopting them however is – who will write them? This ONE BIG Question has kept the ABV adoption way too slow for too long a period in the industry. But no longer..hopefully if your company can invest in right technology. NextOp with its patented “Assertion Synthesis” can provide you high quality properties:

Yunshan, CEO of NextOp will be in John’s Troublemaker panel, so be there to hear him or ask him live at DAC.

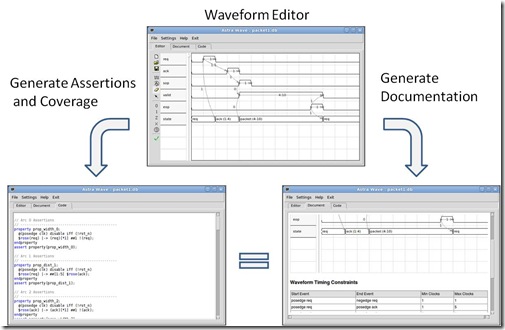

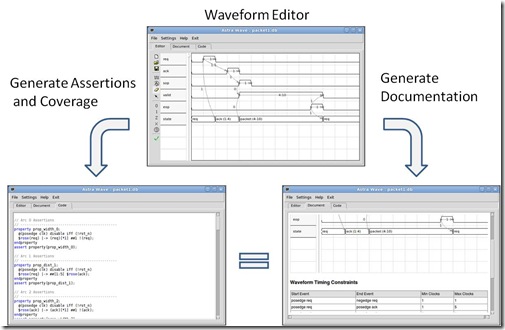

SparkEDA – Ignite your Verification

A quiet storm in the making, SparKEDA spearheaded by Alex Gnusin is creating some very interesting solutions. Its Panda Formal verifier claims simplicity all along. What we really liked on their demo to TeamCVC was their “ASTRA Wave” – an assertion & document creator straight from waveforms, see below for a screenshot. If it works as handy as it promises/claims – this is worth an addition to every Desktop indeed!

Specman is alive & kicking in 2012!

In quite contrast to the very many who believed that Specman & the e-language is dead – it is alive and kicking even well into 2012! See various views at DeepChip pages if you wish. But the ground reality from India and Europe is that there are millions of lines of e-code and more is being written as we speak – some by our own TeamCVC for local customers here who simply refuse to move away from the all powerful IEEE 1647 e-language. The eWG http://standards.ieee.org/develop/wg/eWG.html has recently finished its latest LRM updates (read: http://www.cvcblr.com/blog/?p=333). Cadence continues its updates to Specman with features like:

- Parallel compile

- Compiled mode debug

- Save-restore, reseed on the fly etc.

The latest ClubT was held in Israel in Mar 2012 and hopefully sometime soon in India as well!

Synopsys DAC updates

Since the recent nSys acquisition, Synopsys’s VIP portfolio has become very strong and one can expect more native UVM VIPs from them soon. For DAC 2012 specifically their AMS story sounds interesting: http://bit.ly/KYVIBj

On “Verification Luncheon” they plan to talk about SoC level verification. Sure they would showcase the performance improvements to VCS, but hopefully they will also demo their approach to the manual C-test creation monster soon!

UVM 1.1b is almost there

Most of you are following the UVM development at Accellera and DAC is a great time to release a high quality version of ever growing UVM code base. Learn more about what’s new, and what’s lined up for UVM 1.2 etc. at: http://www.accellera.org/downloads/standards/uvm

What about UVM-like for VHDL users?

If you are a VHDL user and have been feeling let down by the marketing bigwigs of EDA vendors – don’t worry, here is OS-VVM for you: Originating from VHDL guru Jim Lewis through his several years of experience, OS-VMM provides:

- Constrained Random generation

- Coverage Model capturing

all in native VHDL. Add this to the most powerful temporal languages available for hardware design industry – the IEEE 1850 PSL – it is a great compelling solution for VHDL users indeed. BTW – if you didn’t know, VHDL 2008 version already incorporates PSL into it, so you just a VHDL license with your EDA tool to run ABV, CRV & CDV (unlike the relatively expensive SystemVerilog solutions), learn more at: http://www.cvcblr.com/blog/?p=436

Other interesting ones:

Here are some of the other ones you might be interested in:

- EVE – its ZeBu is making more news

- Blue Pearl -relatively new entrant made some noise about generating SDC/Constraints etc.

- Xilinx’s new Vivado is in the news for its latest SystemVerilog additions and all new ISIM simulator. It is yet to be seen how much UVM support they will add in ISM in years to come.

- RealIntent’s X-finder is another niche point tool that some of you may like!

- UVM Linter from AMIQ