Last week, our good friend Gaurav Jalan wrote a nice blog at: http://whatisverification.blogspot.in/2012/08/laws-and-verification.html

He has adapted Murphy’s law into Verification as:

Applying to Verification (http://whatisverification.blogspot.in/2012/08/laws-and-verification.html )

Moore’s law – Amount of code to be verified doubles every 2 years.

Murphy’s law – Any code that isn’t verified will not work.

Now as I recap on last week’s Verilog session delivered to an excited IIT-KGP audience, I realized the same law is applicable to slides/PPT/training too :-) Especially be careful with any code snippet shown in the slides – they could be wrong – unless verified otherwise!

Now back to the title of this blog entry – what are the differences bet’n Verilog’s $display, $monitor & $strobe?

1. Usual answer: $monitor is “continuous monitoring” – Yes, good

For many fresh graduates the detail stops there – but not for those “verilog hungry, pedantic folks”. Here are some more:

1. $monitor & $strobe execute at the POSTPONED region of your Simulator’s event Q – read more about it in LRM or attend our detailed simulation/SVA training (http://www.cvcblr.com/trainings) for more details on this event queues etc.

2. With $display you may get more than display for the same time, for the same signals being displayed – but with $monitor you are guaranteed to get only one at any time for the same display list. As the LRM puts it:

(With $monitor being in use) If two or more arguments change value at the same time, only one display

is produced that shows the new values.

Only one $monitor display list can be active at any one time

The above can be little misleading statement – infact that was the case with our UNVERIFIED PPT slide with some code snippet. Here is a fixed example with some traces:

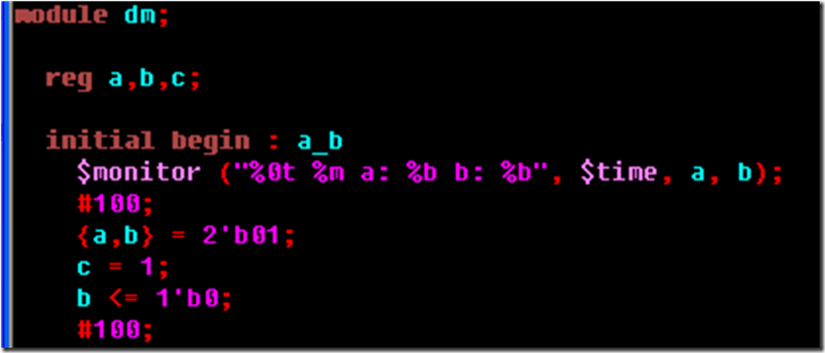

Consider the test vector setup as:

Notice that at time 100 we have “b” being assigned twice – one with BLOCKING and another NBA. With $monitor - you get only one display as guaranteed by LRM. However if we try mimicking the same with always block as below:

Guess what – you get the display twice, see below:

Now a more equivalent mimic would be to use $strobe instead of $display as in:

Now with SystemVerilog there are few more you could expand this topic to including:

1. Use always_comb instead of always @ (*) in the code above – it is guaranteed to wakeup at time 0

2. In the context of SVA (System Verilog Assertions), in 2009 the LRM added “deferred assertions” to handle similar situations.See: http://verificationguild.com/modules.php?name=Forums&file=viewtopic&p=19966 and http://sv-verif.blogspot.in/2012/03/using-systemverilog-assertions-to-check.html

So that was good fun with “details” on what’s usually skipped as “simple stuff” during a Verilog training. Below is full code incase you want to run, modify and experiment around:

No comments:

Post a Comment