As some of our customers ask during our advanced SystemVerilog/UVM training sessions, SystemVerilog doesn’t allow multiple-inheritance. Or to be precise “DID NOT have”, now in SV-2012/2013 it does!

For those yet to get there – here is a quick recap:

Simple inheritance Few derived classes

One can of-course “derive” from another “derived class” too, as-in:

This is used widely in good System Verilog code and in general any OOP code. UVM uses this a lot as many of you who have been fortunate to have attended our popular UVM training sessions (http://www.cvcblr.com/trainings) across the world (Yes, we have delivered across India, various cities, across the globe as in Europe, Asia etc.).

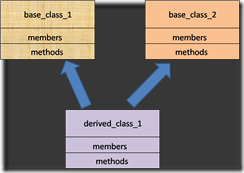

However what was not allowed in older SystemVerilog (2005/2009) is:

Multiple inheritance, as in:

Now one may argue this is not all the time needed etc. If you need to get that interesting debate, a good starting point for you could be: http://en.wikipedia.org/wiki/Multiple_inheritance

Come to think of it, UVM supports TLM ports and that requires multiple inheritance at the core: See the UML diagram for today’s UVM TLM:

i.e. the class uvm_port_base extends (and implements) a standard TLM-INTERFACE class (call it uvm_tlm_if_base). It is also “hierarchical” and can do better with certain characteristics of a uvm_component such as “instance path”, “parent” etc. The current UVM implementation “works-around” the limitation of SV 2005/2009 by instantiating a local uvm_component instance as a member and provides “proxy” methods to mimic the effect of multiple inheritance.

So below is a sample code using Multiple inheritance feature that is now added to P1800-2012 SystemVerilog standard. It does so by introducing few new keywords/constructs:

- interface class

- class implements

In near future your UVM base class could be remodeled as below (not full code obviously):

And voila, the uvm_tlm_port_base implements if_base, port_comp…

As we end 2012, start pushing your friendly EDA vendor for this new stuff as early as Q1-2013! Yes, we have this running at CVC with a popular, leading edge tool!

Happy New Year 2013 to all our readers. Equip yourself with all updates on SystemVerilog by signing up for our upcoming sessions at CVC, contact training@cvcblr.com for more!

No comments:

Post a Comment