With so much fever around SystemVerilog in the verification community, more and more junior engineers are picking up System Verilog. Infact several universities started teaching System Verilog as part of advanced VLSI degree. And with its availability in Desktop based simulators like FPGA design tool chain, more and more FPGA designers are looking at it, and adopting it rapidly.

Clearly SystemVerilog with its all gun blazing features are useful for FPGA community at large, our CTO Srini presented this at FPGA Camp in Bangalore few years ago: http://www.slideshare.net/mobile/fpgacentral/upgrading-to-system-verilog-for-fpga-designs-srinivasan-venkataramanan-cvc

Since then we have trained several FPGA teams on using:

- SystemVerilog for Design (SVD: http://www.cvcblr.com/trng_profiles/CVC_LG_SVD_profile.pdf)

- SystemVerilog Assertions: (SVA: http://www.cvcblr.com/trng_profiles/CVC_LG_SVA_profile.pdf)

- VSV: (http://www.cvcblr.com/trng_profiles/CVC_LG_VSV_profile.pdf)

One of the things we have learnt throughout this journey with FPGA folks is that they care a lot for usability of EDA tools and they are much more demanding than their ASIC Design counterparts on features like:

- IDE – Integrated Design/Development Environment

- Clear cut error messages from the compiler/tool

- Pin point the source file-line easily

While SystemVerilog in its early years was used primarily by ASIC teams the above features were not that critical. But now with 5 EDA vendors supporting SystemVerilog + UVM + SVA, customers are at good position to demand what they need! BTW –who are the 5 EDA vendors?

- Synopsys (www.synopsys.com)

- Mentor (www.mentor.com)

- Cadence (www.cadence.com)

- Aldec (www.aldec.com)

- Axiom (www.axiom-da.com)

And CVC (www.cvcblr.com) is partner with all of them and is uniquely positioned in the world to provide EDA vendor neutral training sessions. Infact recently we have enabled majority of our training labs (See the full list at: http://www.cvcblr.com/trainings) to run on all these 5 tools.

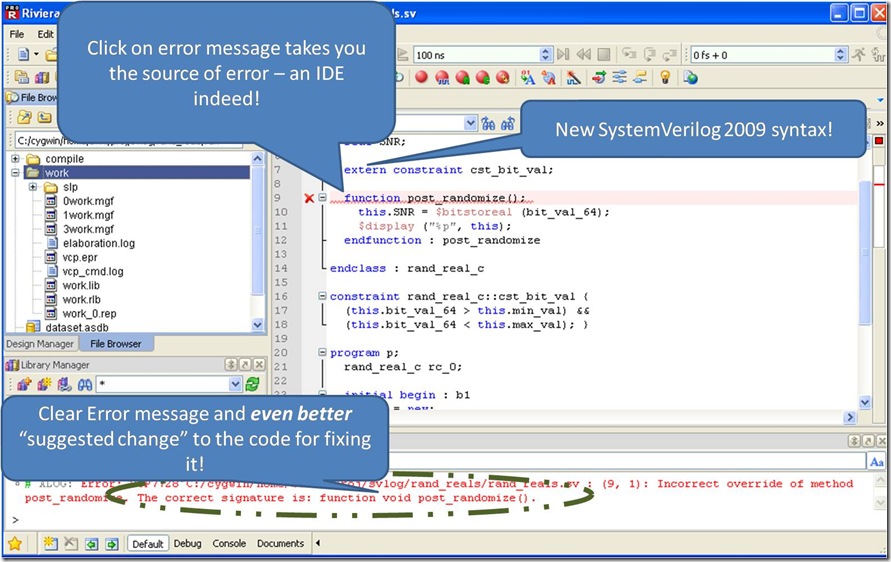

Coming back to the use model requirements, here is a screenshot of how Riviera-Pro from Aldec points a common code error in SystemVerilog. Consider the following piece of code: Can you spot what’s wrong?

Of-course with the “dotted” eclipse, most of you should (if not, we strongly suggest you attend our VSV course ASAP: http://www.cvcblr.com/trng_profiles/CVC_LG_VSV_profile.pdf)

here is a screenshot of how Riviera-Pro from Aldec (www.aldec.com) points a common code error in SystemVerilog.

So – hold no more, even if you are a plain Desktop user with limited budget, SystemVerilog is at your reach!

No comments:

Post a Comment