Earlier this week, Simon Segars, EVP & GM Processor and Physical IP Divisions (http://linkd.in/ThbmbZ) presented an excellent keynote at an invite-only, executive dinner event around the CDNLive India 2012 http://bit.ly/TxallC organized by Cadence. Our CTO Srini (http://linkd.in/e6cSbd)

His theme was around the low power requirements in modern mobile devices (understandably, as the market needs this topic and who is in a better position than ARM can talk about this – being at the center of most of those smartphones!)

In a well drafted, upto-the-point, picture-centric presentation Simon did a great job of explaining what ARM’s big.LIITLE architecture is all about!

As of today, ARM provides Cortex A-15 like cores for the high-end devices:

Quickly ARM realized there is a strong need for low-energy, low-cost cores too to serve the entry level smartphones – here comes the ARM Cortex A-7

Now with lot of data mining and analysis Simon showed a typical pattern that revealed 2 important data points:

- For a whopping 88% of the time in a day, the kind of applications that are run on a smartphone can be done using a processor with speed < 500 MHz

- For the remaining 12% the frequency needs to be > 500 MHz – these are the videos, gaming etc.

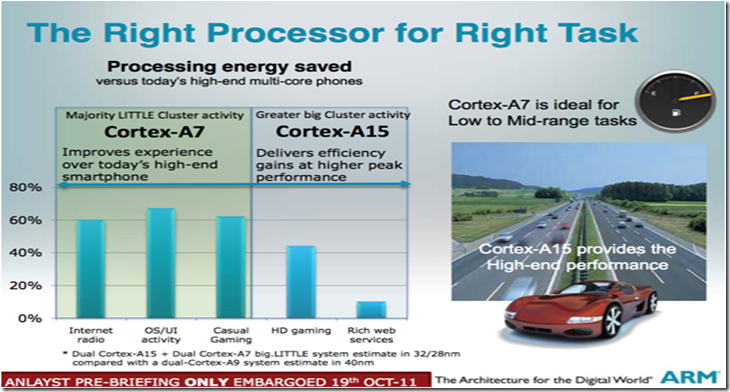

Agreed, your numbers may vary, but the fundamental point is – one could do lot of power saving if we have a big processor to serve the high-end apps and a LITTLE processor to attend to the regular, most-of-the-day work such as MP3 playback, phone calls etc.And this is precisely what ARM’s big.LITTLE architecture is all about – have dual cores with Cortex A-7 & Cortex A-15. I found a slightly older slide on a quick Google search as below (Simon had an updated version of the same)

Now of-course you need multiple teams to take advantage of such an architecture to deliver low power promise to the end user. Simon showed a nice slide listing some of the key stakeholder/steps:

- The system architects to decide which app will run on which core

- The underlying OS to be able to support such a live-scheduling

- The design team to design and implement the various low power techniques such as the DVFS

- The all the more important DV team doing the functional Verification to ensure all the valid power state scenarios are working fine

- Backend team to implement the intended power-save architecture in layout

- Circuit designers to do their bit in choosing various low level power saving techniques

Now going back to our starting question of “Who-will-bell-the-cat” of that “magical low power smartphone chip” – Simon concluded it is ALL-of-us together who need to do this – can’t achieve this level of gains without collaboration!

We at CVC are doing our part of the ecosystem work by developing advanced low power verification training on UPF, CPF modeling, case studies on a UVM SoC Kit etc. So if you are in need of verification training on any of these topics, call us via +91-80-42134156 or training@cvcblr.com