One of the strengths of assertions in SystemVerilog is its well defined sampling semantics. Though it works out-of-the-box and is robust, many users don’t seem to understand it in depth. As we have been blogging on assertions – one needs to be very “pedantic”, i.e. detail oriented to be able to appreciate it, demonstrate it and understand it.

We at TeamCVC have been pioneering assertions as a focus area since our PSL book days (end of 2003, http://www.systemverilog.us/psl_info.html) and it has been almost a decade by now! We cover this in all our training sessions on assertions such as:

- SVA: http://www.cvcblr.com/trng_profiles/CVC_LG_SVA_profile.pdf

- PSL: http://www.cvcblr.com/trng_profiles/CVC_LG_PSL_profile.pdf

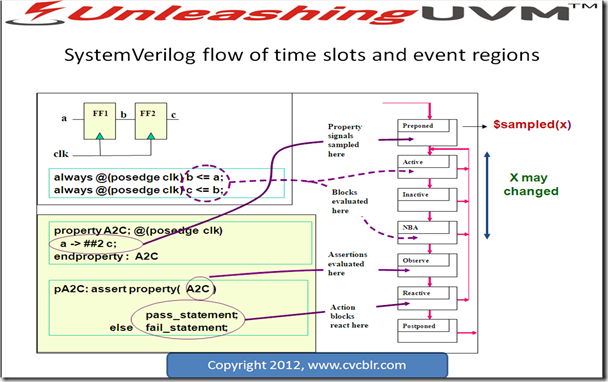

Even during our popular VSV course (http://www.cvcblr.com/trng_profiles/CVC_LG_VSV_profile.pdf) we touch upon this topic during the program block discussion. Below is an extract from our training/book on SVA (http://www.systemverilog.us/sva_info.html):

While the above slide goes well into the depth of this topic, often users ask us if they could “visualize it” inside waveform. Recently we did a SVA class for a VHDL customer who use Questa. Being part of QVP http://www.mentor.com/products/fv/partners/qvp we at CVC have access to Mentor’s latest technologies and this customer insisted that we use Questa during the labs. We enabled more debug sessions including their famous Questa ATV (Assertion Thread Viewer) feature. One of the nice examples our TeamCVC have created explains the events/time-regions nicely. See below for a screenshot:

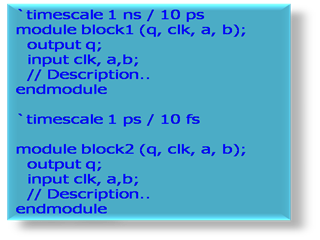

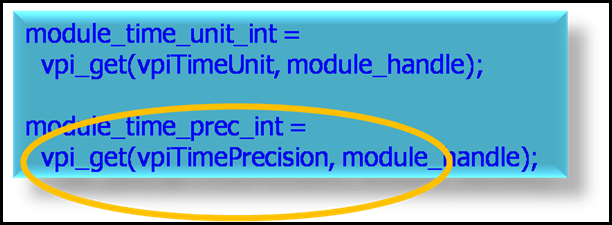

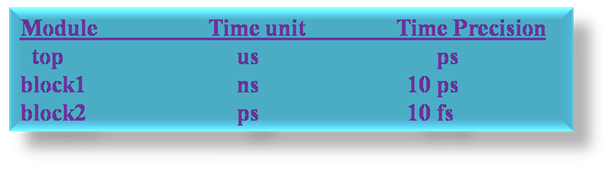

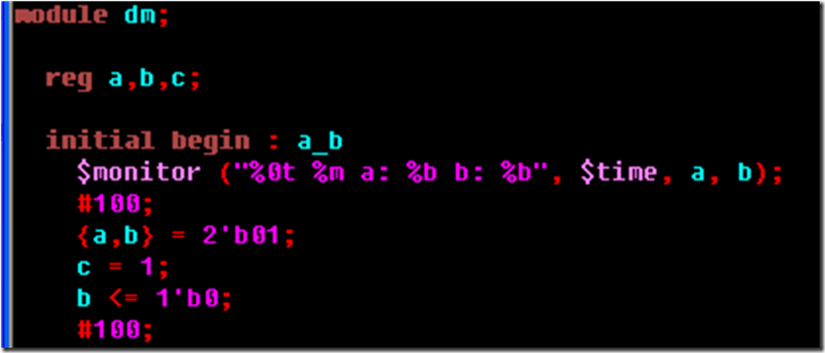

It is almost the same as SystemVerilog LRM’s event Queue – brought inside the waveform, isn’t it! Here is a code snippet for the RTL regions such as “ACTIVE, INACTIVE & NBA” – this is same as in plain Verilog BTW:

Now recall that in testbench with System Verilog there is a program block that executes in REACTIVE region. And so are the assertion action-blocks. And within program block one can do blocking, #0 and NBA ssigns. So how does that get scheduled?

And relevant code-snippet for the REACTIVE assignments:

Putting the full waveform:

NOTE: the “time” doesn’t advance, it is only the DELTAs – Questa is powerful indeed in visualizing it, we will try and add other tool screenshots in near future if there is enough demand from you – our beloved readers!

Before we close, here is what a full, IDE (Integrated Development Environment) that Questa provides for this:

Hope you enjoyed this “flow of events” and the power of “visualizing” it – as much as we did. Drop your comments below!

Signing off with confidence, it is TeamCVC!