Are you an avid fan of CRV – Constraint Random Verification? Have you played enough with System Verilog constraints? Many of our customers having attended our regular VSV training (http://www.cvcblr.com/trainings) do become so! One of the nice features of SystemVerilog constraint mechanism is its “bi-directionality” – a key feature that makes the distribution fairly wide spread and makes the state space well covered.

The industry has learnt it over the last decade of CRV usage – bidirectional constraints are better than unidirectional ones (that was the default in previous generation solver inside popular tool like Specman – called PGen. Even Specman has moved to a more robust, bi-directional IGEN/Intelligen few years back).

In SV this bi-directionality is subtle. Consider the code below:

To an average SV engineer the above 2 constraints look “same” as the function is trivially doing a return job. However they are different for an avid SV user or a solid SV solver such as Questa from Mentor. As per LRM:

Random variables used as function arguments shall establish an implicit variable ordering.

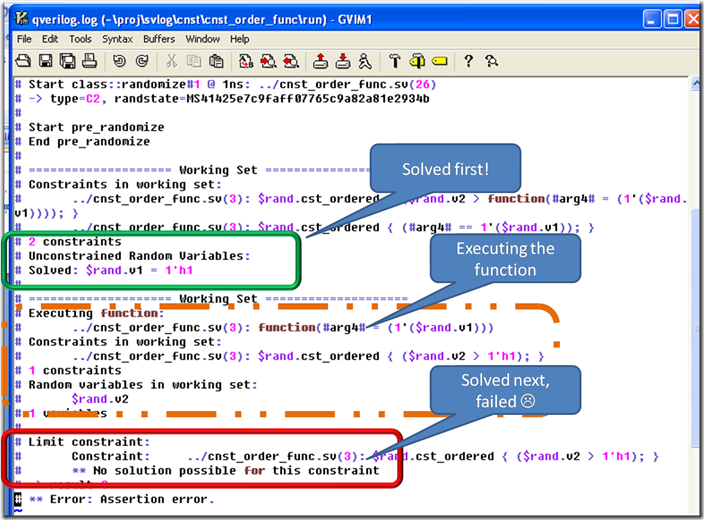

Hence in case of “cst_ordered”, the variable “v1” is solved FIRST and then the “v2” – i.e. they are solved separately and not together (Which is what happens with ‘cst_bidir”).

So what’s the big deal? Consider “v1” is chosen to be “1” first, then the solver has NO solution for “v2” :-( leading to a constraint failure.

So, next time when you use a function in a constraint, remember/recall/read this blog :-)

Care for a proof? See what Questa’s solveverbose prints:

qverilog file.sv –R –solveverbose=2

Enjoy CRV, enjoy SystemVerilog. In case you want to delve deeper into SV, do call us via training@cvcblr.com

No comments:

Post a Comment