Here is a nice Verilog VPI (Verilog Procedural Interface a.k.a PLI 2.0) app that we mentioned during our just concluded Verilog training at CVC.

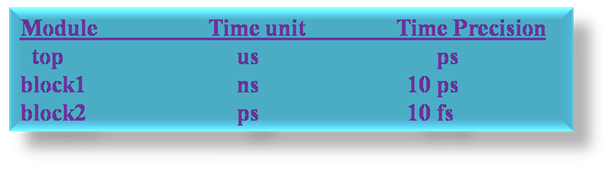

This application just walks through the complete design hierarchy and spits out the Timescale information for each module. It is quite handy to find which module has the least timescale precision value (and hence controls the whole simulation) for e.g. when the design has been given as a compiled database or a protected one – simple grep/PERL kind of ideas maynot fit. This application will extract:

- The module name

- Its Time Scale value

- Its TimePrecision value

Here is a PLI task named " $print_timescale " which if called on a top level module will print this information for the entire hierarchy.

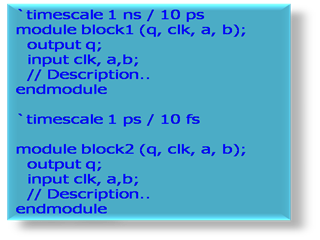

The following Verilog code (which could be the top level of your design, or TB) shows how to use such a task.

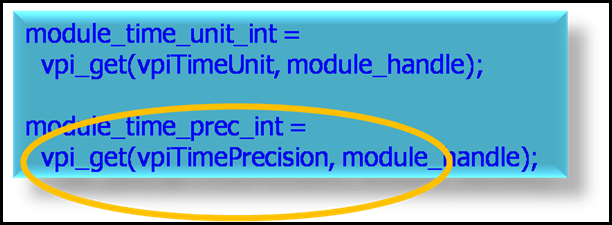

Needless to say the hierarchy can be very deep and totally encrypted etc. It is all about tree traversal and printing the relevant portions of vpi_get as in:

Following is a code snippet from the VPI/PLI C-code:

Now wrap that inside a tree walker code that would walkdown your Verilog hierarchy (post elaboration) such as:

At each node, print the results.

Drop us a note in the comments below if you would like to see the complete VPI code listing!

Who said Verilog is simple – it can become very interesting with large designs with interesting challenges!

Now you see why CVC is in the best of Verification related technology when it comes to training engineers (freshers/experienced alike) – where else would engineers get to experiment and learn at their own pace all the way from UNIX, Verilog to SystemVerilog, Assertions, UVM and beyond? See http://www.cvcblr.com/trainings for more!

1 comment:

Time management plays a major role for the success of business.Hence i would like to use Verilog PLI/VPI in our business.

Hierarchy

Post a Comment