As we wrap up 2012 with yet another successful VSV course at CVC today’s topic was IPC in System Verilog. As most of the attendees in this session are young engineers, they have a constant thirst for knowledge and demand more. We at CVC love that challenge. Based on last few sessions we created more smaller examples around threads, mailboxes for the engineers to play around with. Here are some of the meddling around experiments you may do with Mailboxes in SV.

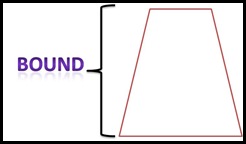

To start with – the size of the mailbox – a.k.a the DEPTH of the FIFO: Here is how you configure the same (the formal argument is named as bound by LRM):

And we had some interesting discussion around the bound & num() - similar to FIFO’s DEPTH and LEVEL:

To get the code part of it straight, here is what LRM has on these 2 methods:

function new (int bound = 0);

i.e. the constructor for mailbox has an argument that’s defaulted to 0 – be careful with it, this could lead to memory leaks from user code (See: http://www.cvcblr.com/blog/?p=29 )

The summary there – use sized mailbox always. This would fix the DEPTH of the FIFO or the Mailbox:

Now there is a method to get the “current level” of the Mailbox, with prototype:

function int num ();

Here is a pictorial way to explain its usage:

To look at some SystemVerilog code:

And to close this article with more pictures than usual – be careful with generic mailboxes – i.e. those with no explicit parameterization. Avoid them if you can, watch this space www.cvcblr.com/blog for an upcoming article on that.

Do more with SystemVerilog! And do call us via training@cvcblr.com in case you want to learn SystemVerilog the right way!

No comments:

Post a Comment